IC 74193 is a 4-bit presettable synchronous MODULO-16 Up/Down binary counter IC. IC74193 has two separate clock input pins to count up and count down, the output is synchronous with the clock inputs. The separate Terminal Count Up & Terminal Count Down are provided which is useful for designing higher counter or cascading the IC74193. The master reset pin is provided to reset the whole IC & also an active low parallel load input pin is available to start counting with any number. The above terms we will explain briefly in the functional description with the help of the datasheet & block diagram of IC 74LS193. There are some very important words/concepts/terms which you should always keep in mind while learning about counter find best-ever explain on the internet of those terms on my blog “IC7490 Decade counter“.

Features of IC74193:

- 4-bit presettable synchronous up/down counter.

- It has an individual Preset input Pin by using this we can load any count and start the counting from that loaded number.

- Cascading can be used to design mod-n counter (where n = 0, 1, 2, 3,…………., infinity).

- Modulo-16 counter (However the counting is not limited to 16 we can increase the counting by cascading two or more IC74193).

- Low Power . . . 95 mW Typical Dissipation.

- High Speed . . . 40 MHz Typical Count Frequency.

- Input Clamp Diodes Limit High-Speed Termination Effects.

What is Meant by Presettable? In IC74193 a predefined number/count can be loaded by using its preset pins and supplying a low logic to the Parallel Load(PL) pin, hence this IC is known as presettable IC.

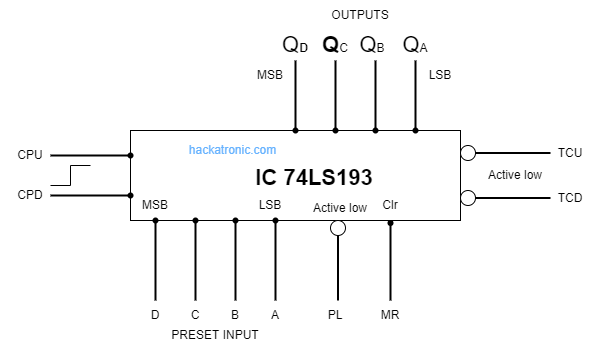

Block Diagram of IC74193:

The simplest block diagram of IC74193 is shown in the following figure.

| Pin | Description |

| CPU | Count up clock pulse input |

| CPD | Count down clock pulse input |

| MR | Asynchronous Master Reset(Clear) input |

| PL̅ | Asynchronous Parallel Load(Active Low) Input |

| TCU | Terminal count Up(Carry) output |

| TCD | Terminal count Down(Borrow) output |

| A,B,C, & D | Preset Inputs(Parallel Data Inputs) |

| Qn | Flip-Flop Outputs |

Functional Description of IC74193:

- The flip-flop output pins are Qn(Qa, Qb, Qc, & Qd).

- The A, B, C, & D are the preset pins whatever count will be loaded to the preset pins will reflect as flip-flop output

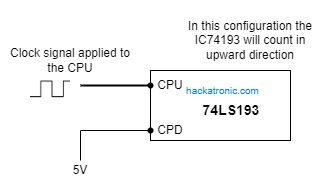

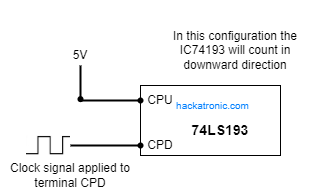

CPU & CPD Clock Terminal:

- For Up counters, the CPU(count up) is connected with clock signals and CPD is connected to logic high(5V).

- And Similarly, for the down counter, the CPD is connected to clock signals, and the CPU is connected to logic high(5V). The below figures are the diagrammatic representation for the Up/Down Counter.

Master Reset (MR):

- The Master Reset (MR) terminal is used to reset the IC or to clear the IC output by applying a high signal.

- A HIGH signal on the Master Reset input will disable the preset gates, override both Clock inputs, and latch each Q output in the LOW state. If one of the Clock inputs is LOW during and after a reset or load operation, the next LOW-to-HIGH transition of that Clock will be interpreted as a legitimate signal and will be counted.

Parallel Load (PL)

- The Parallel Load (PL) is an active-low input pin this is used to load data into the IC.

- Each circuit has an asynchronous parallel load capability permitting the counter to be preset.

- When the Parallel Load (PL) and the Master Reset (MR) inputs are LOW, information present on the Parallel Data inputs (A, B, C, D) is loaded into the

counter and appears on the outputs regardless of the conditions of the clock inputs.

Terminal Count Up (TCU) and Terminal Count Down (TCD):

- Terminal Count Up (TCU) and Terminal Count Down (TCD) are also active low output pins, the output is always High, it goes Low once IC reaches too its max & min count.

- When a circuit has reached the maximum count state (9 for the LS192, 15 for the LS193), the next HIGH-to-LOW transition of the Count Up Clock will cause TCU to go LOW. TCU will stay LOW until CPU goes HIGH again, thus effectively repeating the Count Up Clock, but delayed by two gate delays.

- Similarly, the TCD output will go LOW when the circuit is in the zero states and the Count Down Clock goes LOW.

- Since the TC outputs repeat the clock waveforms, they can be used as the clock input signals to the next higher-order circuit in a multistage counter.

- The truth table for these pins is given in the below table.

| For Up Counter | |||||

| QD | QC | QB | QA | TCU | TCD |

| 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 |

| … | … | … | … | … | … |

| 1 | 1 | 1 | 1 | 0 | 1 |

| For Down Counter | |||||

| 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 |

| … | … | … | … | … | … |

| 0 | 0 | 0 | 0 | 1 | 0 |

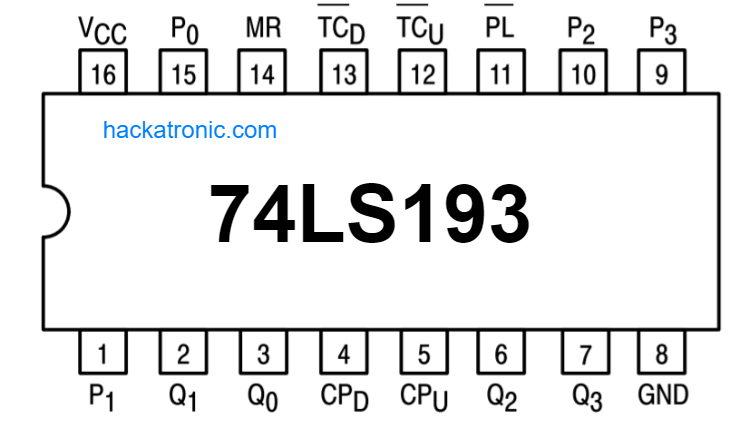

Pin Configuration:

| Pin No. | Pin Name |

| 1 | P1 ~ B |

| 2 | Q1 ~ QB |

| 3 | Q0 ~ QA |

| 4 | CPD |

| 5 | CPU |

| 6 | Q2 ~ QC |

| 7 | Q3 ~ QD |

| 8 | GND |

| 9 | P3 ~ D |

| 10 | P2 ~ C |

| 11 | PL̅(Active Low) |

| 12 | TCU̅(Active Low) |

| 13 | TCD̅(Active Low) |

| 14 | MR |

| 15 | P0 ~ A |

| 16 | VCC |

Find datasheet on IC74193 Datasheet